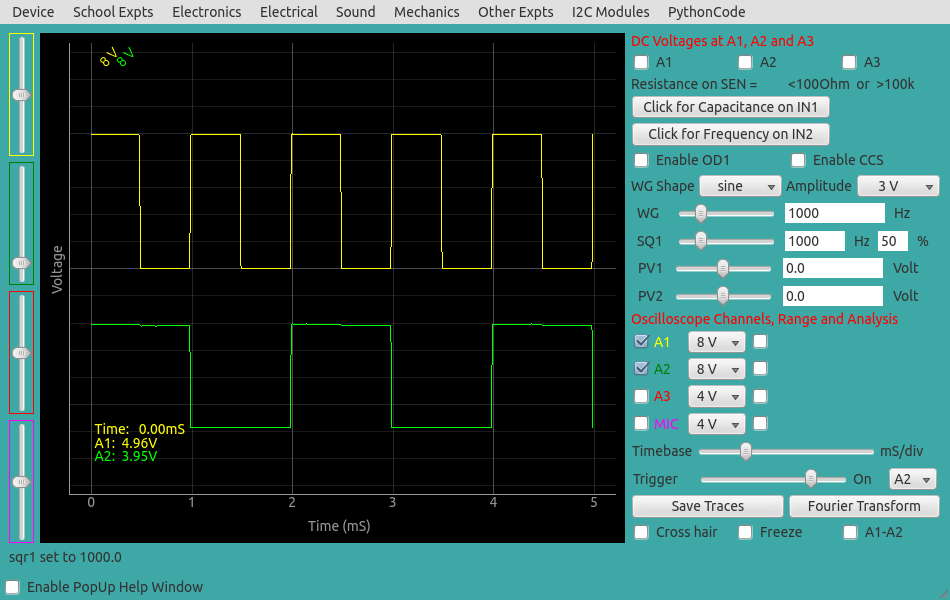

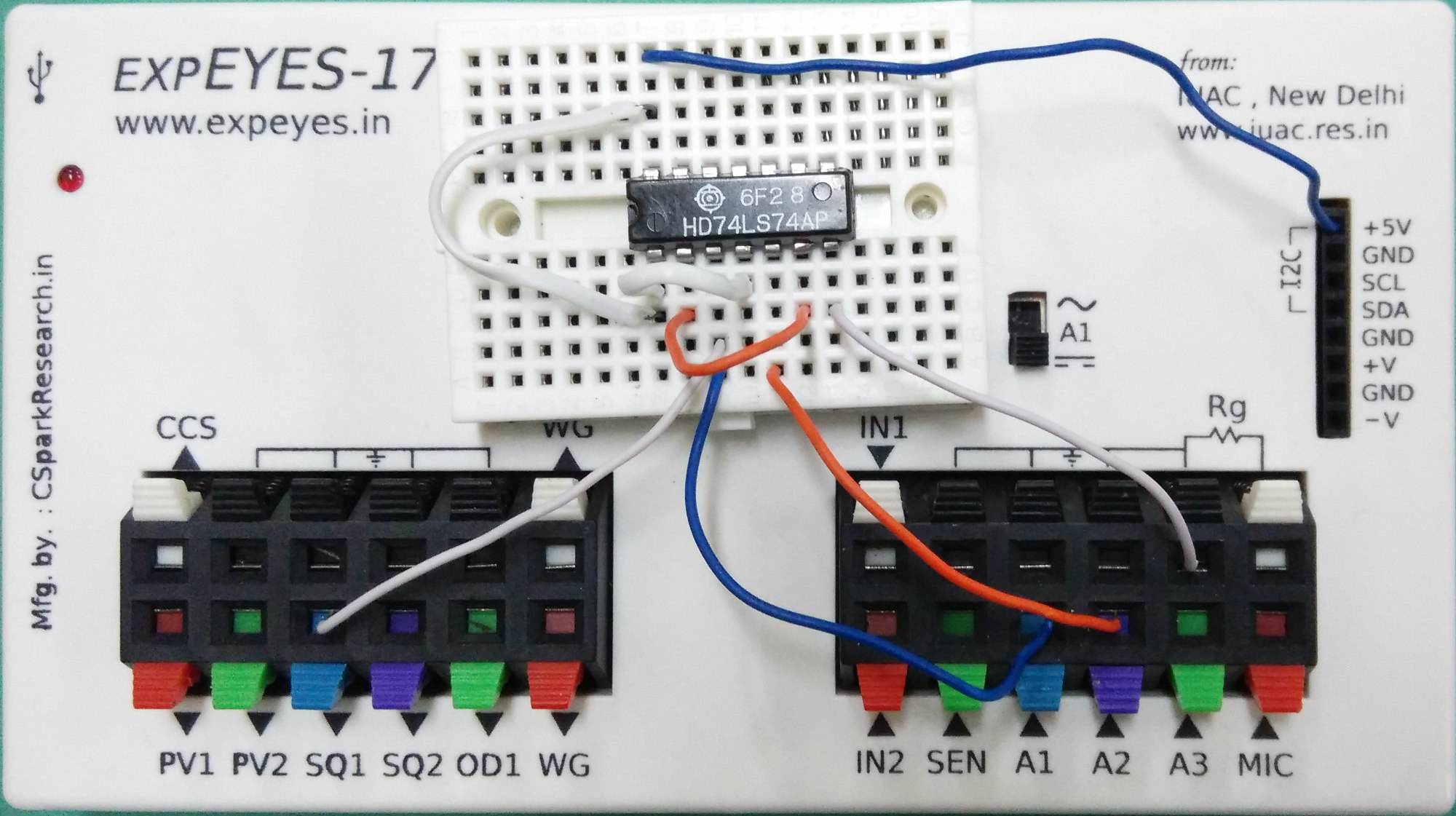

A square wave is given to the clock input of the 74LS74 flipflop. The Q-bar output is connected to the D input. Clear and Preset inputs should be held HIGH. Every rising edge toggles the output, but the falling edge is uneventful.

May 03, 2019

Jithin B.P.

Jithin B.P.